What’s the difference between FPGA and other programmable devicces?

Field Programmable Gate Arrays (FPGAs) are digital ICs composed of arrays of logic blocks that can be programmed (wired) and reprogrammed multiple times, even after the product containing the FPGA has been shipped and “in the field.” FPGA is not a monolithic technology; there are differences in FPGA structure and programming methods, packaging methods, and integration levels. Moreover, FPGAs are not the only programmable logic devices available to designers. This article mainly compares the differences between FPGAs and other programmable devices.

An FPGA consists of a set of logic blocks surrounded by programmable input/output (I/O) blocks with a layer of programmable interconnect. FPGAs have several sub-architectures, some of which are discussed below. Optimizing FPGA performance in any particular application depends on selecting the correct device with the required logic blocks in an efficient architecture and optimizing the interconnect routing.

Compared to other programmable logic devices, such as simple programmable logic devices and complex programmable logic devices (both discussed below), FPGAs offer the highest logic capacity and performance. A typical FPGA can contain tens of thousands of logic blocks and the same number of flip-flops. FPGAs can be differentiated based on several factors, such as the relative size of the logic blocks they are composed of and the various interconnect technologies used.

FPGA logic architecture

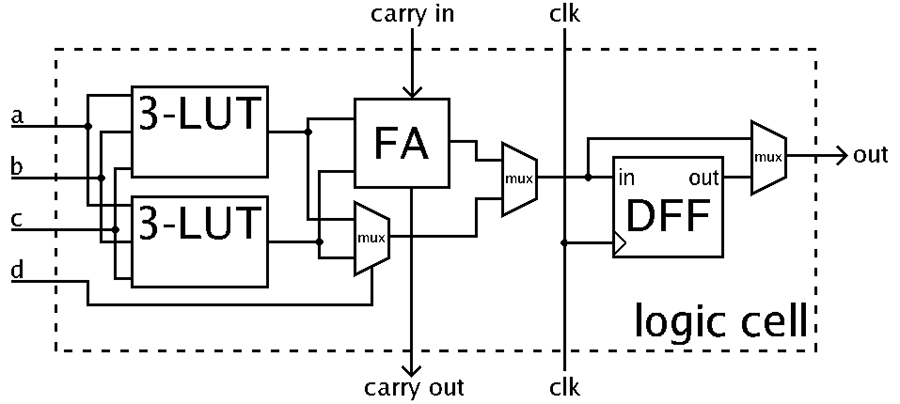

There are two broad categories of FPGA logic architectures, coarse-grained and fine-grained. Each architecture is suitable for different classes of applications. A large block of logic in a coarse-grained FPGA typically consists of two or more lookup tables and two or more flip-flops. These FPGAs typically include a four-input loop table that performs logic functions. Coarse-grained FPGAs sacrifice higher performance for specific functions than fine-grained implementations, but coarse-grained implementations offer less flexibility. Coarse-grained FPGAs are typically optimized for certain classes of applications, such as those that require heavy floating-point computations.

Fine-grained FPGAs have a large number of simple logic blocks, usually containing a two-input logic function or a 4-to-1 multiplexer and a flip-flop. These devices are ideal for executing systolic logic, where programmable interconnects can handle processing dependencies, and highly parallel data flows do not require sequential management. Systolic arrays (and FPGAs) can be used in applications such as artificial intelligence, image processing, pattern recognition, and more.

Many of today’s FPGAs combine coarse-grained elements in a fine-grained programmable fabric. Coarse-grained elements are also known as “hard blocks”. They can include functions ranging from multipliers, high-speed I/O and embedded memory to gigabit transceivers, complete DSP blocks and embedded ARM processors. Independent of the programmable fabric, these hard blocks provide ASIC-level performance and efficiency without consuming fabric resources, making the FPGA fabric available for application-specific functions.

FPGA programming and interconnection

In addition to the differences between fine-grained and coarse-grained logic architectures, there are also differences in the process technologies used to manufacture FPGAs. Most FPGAs use static memory (SRAM) or anti-fuse CMOS technology. SRAM-based FPGAs are in-system programmable, while antifuse-based FPGAs are one-time programmable. SRAM-based FPGAs are typically higher density devices, while antifuse devices typically contain a richer density of programmable interconnects.

SRAM FPGAs are reprogrammable in the field after the system ships, but require an external configuration memory source. Antifuse FPGAs do not require external configuration memory. The configuration memory used with SRAM devices contains a router that defines how all the FPGA elements are interconnected. At startup, the FPGA can load its configuration memory, or an external processor can load it. The configuration time is usually under 200ms.

Antifuse FPGAs retain their program when powered down, but they can only be programmed once. Programming of SRAM and antifuse devices can be performed by the FPGA manufacturer, distributor, or system manufacturer.

3D Packaging and Heterogeneous FPGAs

To continue to shrink the size and power consumption of advanced FPGAs, manufacturers have adopted 3-dimensional (3D) or stacked architectures. When packaging multiple dies and FPGAs, two approaches are generally used. In one case, multiple FPGA dies are packaged on a single piece of silicon, providing interconnects between the dies. The multi-die structure enables different process technologies to fabricate specific parts of the FPGA to optimize overall performance. An FPGA composed of multiple dies is called a heterogeneous FPGA.

Advances in 3D integration and packaging have enabled complex system-in-package (SiP) implementations consisting of multiple IC technologies, helping to overcome the limitations of Moore’s Law. Through innovations in stacking technology, the ability to fabricate and package homogeneous and heterogeneous 3D ICs has overcome power, cost and interconnect constraints. These new SiP technologies can support emerging high-performance system requirements, namely very high interconnect bandwidth and lowest power consumption per bit.

![]()

simple programmable logic device

As the name suggests, Simple Programmable Logic Devices (SPLDs) are small and simple programmable devices. They are the simplest form of programmable logic devices and are known by many names, including General Array Logic (GAL), Programmable Logic Array (PLA), and Programmable Array Logic (PAL). Although they are simple, SPLDs are very flexible and are often used to replace logic components such as 7400 series TTL devices.

SPLDs consist of a series of up to 24 macrocells that contain combinations of logic functions such as AND and OR gates and flip-flops. Each microcell can execute a simple Boolean logic equation, which, if necessary, can be stored in flip-flops until the next clock cycle. Like FPGAs, SPLDs can use fuses or various types of nonvolatile memory cells to define functionality. SPLDs offer several advantages over 7400 series device:

- A single SPLD requires less power, simpler wiring and takes up less board space than the several 7400 devices it replaces.

- SPLDs are flexible (and reprogrammable), so updating or changing logic does not require board changes. and can also replace one SPLD with another SPLD programmed to a different design to change the logic.

- SPLDs can be used for various functions such as device-to-device interfacing, signal processing, decoding, data display, and timing and control operations.

complex programmable logic device

Although much more complex than SPLDs, complex programmable logic devices (CPLDs) typically have much less processing power than FPGAs and are built using a different architecture. The structure of CPLDs is not as flexible as that of FPGAs, with only a few logic arrays providing a relatively small number of clock registers. However, CPLDs have more predictable timing delays and generally have denser logic interconnect structures. CPLDs are logic-based, while FPGAs are interconnect-based.

FPGAs are more flexible, but more complex to design, and FPGAs tend to be larger than CPLDs. FPGAs often contain complex embedded functions such as memory, serializers/deserializers, analog front ends, and more. CPLDs almost always have embedded flash to store their configuration, which is usually not the case with FPGAs. FPGAs require external non-volatile memory to store their programming.

Systems that require logic already configured at startup typically use CPLDs. CPLDs and FPGAs can also be used in the same system. The CPLD performs the glue logic functions and starts the FPGA, and can be used to control the startup and reset functions of the entire system, while the FPGA performs all the heavy processing functions.

Application specific integrated circuits

FPGAs also compete with application-specific ICs (ASICs) and application-specific standard parts (ASSPs). Systems that previously required multiple ASICs and/or ASSPs can now use a single FPGA. Compared to multi-chip solutions, a single FPGA can provide lower power requirements, higher speed, less board space, and can be reconfigured even after the product ships.

In some applications, ASICs and ASSPs can offer advantages over FPGAs. In high-volume applications, ASICs and ASSPs may cost less than FPGAs. Some designers use FPGAs during product development to take advantage of their flexibility during design iterations, moving the final design into an ASIC so it cannot be modified after the design is complete, improving system security.

Another product category is FPGAs embedded in ASICs. These devices, called eFPGAs, combine the security benefits of ASICs with some of the flexibility of FPGAs. eFPGAs can be scaled to meet specific application needs. eFPGAs can extend the life of ASICs by providing programmability for functions such as algorithms and protocols that can evolve over the life of the system.

FPGAs are the most complex digital ICs that can be reprogrammed. ASICs and ASSPs can be more complex than FPGAs but are not reprogrammable. SPLDs and CPLDs are reprogrammable but much simpler compared to FPGAs. FPGAs are used in a growing number of applications due to their high performance and programmability.