Power Design and Implementation Of Xilinx FPGA

Do you know how to design the power supply for Xilinx chips? Do you need professional Xilinx professional chip design guidance? As a professional supplier of chips and electronic components, Haoxinsheng has many years of professional experience in this field. This article mainly introduces the power supply design of Xilinx FPGA, including power supply types, voltage requirements, power consumption requirements, power-on and power-on sequence requirements, and common power supply implementation schemes.

Xilinx FPGA voltage types and requirements

With the development of FPGA, its voltage types are more and more abundant, mainly including the following types:

The processor system voltage mainly supplies power to the ARM in the Zynq series SoC, including VCC_PSINTFP, VCC_PSINTLP, VCC_PSAUX, VCC_PSINTFP_DDR, VCC_PSADC, VCC_PSPLL, VPS_MGTRAVCC, VPS_MGTRAVTT, VCCO_PSDDR, VCC_PSDDR_PLL, VCCO_PSIO, VCC_PSBATT, etc.;

FPGA Logic voltage, which mainly supplies power to the FPGA logic part, including VCCINT, VCCINT_IO, VCCBRAM, VCCAUX, VCCO, VCCAUX_IO, VBATT, etc.;

GTx Transceiver voltage, which mainly supplies power to the GTx high-speed transceivers in the FPGA part, including VCCINT_GT, VMGTAVCC, VMGTAVTT, VMGTVCCAUX, VMGTAVTTRCAL;

System Monitor voltage, which mainly supplies power to the ADC in the FPGA part, including VCCADC and VREFP;

High Bandwidth Memory voltage, including VCC_HBM, VCC_IO_HBM, VCCAUX_HBM;

VCU voltage, only available on Zynq UltraScale+ MPSoC series devices with image processing core, including VCCINT_VCU;

RF voltage, only available in Zynq UltraScale+ RFSoC series, including VADC_AVCC, VADC_AVCCAUX, VDAC_AVCC, VDAC_AVCCAUX, VDAC_AVTT, VCCINT_AMS, VCCSDFEC;

The power supply objects of the above various voltages are different, and the accuracy requirements are also different. For FPGAs with different architectures, the voltage accuracy requirements are also different. The ripple range varies from 2% to 5%, but the overall requirements are It is relatively high, but the current requirements are getting larger and larger. For example, VCCINT can reach a maximum of tens of amps. At the same time, various voltage values are different, some can be combined, and some cannot be combined, and timing control is also required.

For Zynq UltraScale+ MPSoC (ZU+ MPSoC), Zynq UltraScale+ RFSoC (ZU+ RFSoC), Zynq 7000 (Z7), UltraScale+ (US+ includes VU+ and KU+), UltraScale (US includes VU and KU), 7 series, etc., for each type The voltage, required voltage value and accuracy are listed in the following table:

| Voltage Type | ZU+ MPSoC | ZU+ RFSoC | Z7 | US+ | US | 7 Series | |

| Logic | VCCINT | 0.85(3%) | 0.85(3%) | 1.0(3%) | 0.85(3%) | 0.95(3%) | 1.0(3%) |

| 0.72(3%) | 0.72(3%) | 0.95(3%) | 0.72(3%) | 0.9(2.2%)KU | 0.9(3%) | ||

| 0.9(3%) | 0.9(3%) | 1.0(3%) | 0.95(2%) | ||||

| The three series of AKV are different | |||||||

| VCCINT_IO | 0.85(3%) | 0.85(3%) | × | 0.85(3%) | 0.95(3%) | × | |

| 0.9(3%) | 0.9(3%) | 0.9(2.2%)KU | |||||

| 1.0(3%) | |||||||

| VCCBRAM | 0.85(3%) | 0.85(3%) | 1.0(3%) | 0.85(3%) | 0.95(3%) | 1.0(3%) | |

| 0.9(3%) | 0.95(3%) | 0.9(3%) | 1.0(3%) | 0.9(3%) | |||

| 0.95(3%) | |||||||

| The three series of AKV are different | |||||||

| VCCAUX | 1.8(3%) | 1.8(3%) | 1.8(5%) | 1.8(3%) | 1.8(5%) | ||

| VCCO | √ | √ | √ | √ | √ | √ | |

| VCCAUX_IO | 1.8(3%) | 1.8(3%) | 1.8(5%) | 1.8(3%) | 1.8(5%) | ||

| 2.0(3%) | 2.0(3%) | ||||||

| A7没有 | |||||||

| VBATT | √ | √ | √ | √ | |||

| GTx | VCCINT_GT | × | × | × | 0.85(3%) | × | × |

| 0.9(3%) | |||||||

| 只有VU+才有 | |||||||

| VMGTAVCC | 0.9(3%) | 0.9(3%) | 1.0(0.97~1.08) | 0.9(3%) | 1.0(3%) | 1.0(0.97~1.08) | |

| 1.05(1.02~1.08) | 1.03(3%)VU | 1.05(1.02~1.08) | |||||

| VMGTAVTT | 1.2(3%) | 1.2(3%) | 1.2(2.5%) | 1.2(3%) | 1.2(2.5%) | 1.2(2.5%) | |

| 1.23(2.4%)VU | |||||||

| VMGTVCCAUX | 1.8(3%) | 1.8(3%) | 1.8(2.7%) | 1.8(3%) | 1.8(2.7%) | 1.8(2.7%) | |

| VMGTAVTTRCAL | 1.2(3%) | 1.2(3%) | 1.2(2.5%) | 1.2(3%) | 1.2(2.5%) | 1.2(2.5%) | |

| 1.23(2.4%)VU | |||||||

| System Monitor | VCCADC | 1.8(3%) | 1.8(3%) | 1.8(5%) | 1.8(3%) | 1.8(5%) | |

| VREFP | 1.25(4%) | 1.25(4%) | 1.25(4%) | 1.25(4%) | 1.25(4%) | ||

| Processor System | VCC_PSINTFP | 0.85(5%) | 0.85(5%) | VCC_PSINT(1.0(5%)) | |||

| 0.9(3%) | |||||||

| VCC_PSINTLP | 0.85(5%) | 0.85(5%) | |||||

| 0.9(3%) | |||||||

| VCC_PSAUX | 1.8(5%) | 1.8(5%) | 1.8(5%) | ||||

| VCC_PSINTFP_DDR | 0.85(5%) | 0.85(5%) | × | ||||

| 0.9(3%) | |||||||

| VCC_PSADC | 1.8(5%) | 1.8(5%) | × | ||||

| VCC_PSPLL | 1.2(3%) | 1.2(3%) | 1.8(5%) | ||||

| VPS_MGTRAVCC | 0.85(3%) | 0.85(3%) | × | ||||

| VPS_MGTRAVTT | 1.8(3%) | 1.8(3%) | × | ||||

| VCCO_PSDDR | DDR I/O | DDR I/O | DDR I/O | ||||

| VCC_PSDDR_PLL | 1.8(5%) | 1.8(5%) | × | ||||

| VCCO_PSIO | MIO | MIO | MIO | ||||

| VCC_PSBATT | √ | √ | × | ||||

| HBM | VCC_HBM | 1.2(3%)VU+ | |||||

| VCC_IO_HBM | 1.2(3%)VU+ | ||||||

| VCCAUX_HBM | 2.5(3%)VU+ | ||||||

| VCU | VCCINT_VCU | 0.9(3%) | |||||

| RF | VADC_AVCC | 0.925(3%) | |||||

| VADC_AVCCAUX | 1.8(3%) | ||||||

| VDAC_AVCC | 0.925(3%) | ||||||

| VDAC_AVCCAUX | 1.8(3%) | ||||||

| VDAC_AVTT | 2.5(3%) | ||||||

| 3.0(3%) | |||||||

| VCCINT_AMS | 0.85(3%) | ||||||

| VCCSDFEC | 0.85(3%) | ||||||

Power Design for Xilinx FPGAs

The power consumption of FPGA includes internal resources such as the number of logic cells/BRAM used, operating clock frequency, switching rate, routing and I/O power consumption, etc. For I/O power consumption, the influencing factors include output type, operating clock frequency, and the number of output signal inversions and output load. Actual power consumption depends on the specific system design. This part mainly focuses on the power consumption of the FPGA logic part. For the Zynq series, due to different operating systems and different applications, detailed calculations cannot be performed, but a rough evaluation can be performed through software.

The total power consumption of the entire FPGA design consists of three parts: chip static power consumption, design static power consumption, and design dynamic power consumption

Chip static power consumption: The power consumption when the FPGA is not configured after power-on is completed, mainly the power consumption consumed by the leakage current of the transistor.

Design static power consumption: After the FPGA configuration is completed, when the design has not started, it is necessary to maintain the static current of I/O, the static power consumption of clock management and other parts of the circuit.

Design dynamic power consumption: The power consumption of the design after the design in the FPGA is started normally; the power consumption of this part mainly depends on the level used by the chip and the occupancy of the internal logic and routing resources of the FPGA.

1. Standby power consumption (chip static power consumption)

Due to leakage currents, the device also consumes energy during standby. Standby power consumption varies with the size, temperature and process of the chip DIE. Standby power consumption can be modeled using device characterization parameters and defined into two categories: typical power consumption and maximum power consumption.

2. IO power consumption (design static power consumption)

The I/O power dissipation is the VCCO power dissipation, mainly from the external load capacitors connected to the output pins of the device, the impedance mode output driver circuit, and the charge and discharge currents of the external matching network (if any).

As mentioned earlier, part of the VCCO power consumption is actually consumed inside the FPGA, and another part of the energy is consumed by the external matching resistor network and the output capacitor load. Designers should consider the internal power dissipation of the VCCO when planning a thermal solution. As part of the output power of the VCCO power supply, designers should also consider the composition of external power dissipation.

3. Dynamic power consumption (design dynamic power consumption)

Dynamic power dissipation inside the device occurs when an internal node changes logic state (eg, from logic 0 to logic 1) because it requires energy to charge and discharge the internal capacitances of the logic array and interconnect. Core dynamic power includes logic cell power and wire power. The LE power dissipation comes from the charge and discharge of the internal node capacitance and the current consumption of the internal resistor unit. Wire power dissipation comes from the charge and discharge currents each LE drives as it drives the external wire capacitance. The core dynamic power consumption mainly comes from the following structural units:

LUTs

RAM module

DSP Slice

Phase Locked Loop (PLL)

clock tree network

GTx transceiver

IP usage

IO usage

4. Power consumption design

The power consumption of the first two parts depends on the FPGA chip and the hardware design itself, and it is difficult to improve greatly. What can be optimized is the power consumption of the third part: design dynamic power consumption, which accounts for more than 90% of the total power consumption. Therefore, reducing the design dynamic power consumption is a key factor in reducing the power consumption of the entire system.

Tjmax”θJA*PD+TA

where Tjmax represents the maximum junction temperature of the FPGA chip; θJA represents the junction to ambient thermal resistance between the FPGA and the surrounding atmosphere, in °C/W; PD represents the total power dissipation of the FPGA. , the unit is W; TA represents the ambient temperature.

Taking the XC7K325T-2FFG900I series chip as an example, θJA=9.7°C/W, in the environment of TA=55°C, if the junction temperature Tjmax does not exceed 100°C, the total power consumption of the FPGA can be calculated as:

PD<(Tjmax-TA)/θJA=(100-55)/9.7=4.639W

Therefore, as long as the actual power consumption exceeds this value, optimization processing is required. There are two main methods for optimization processing: one is to reduce θJA: the thermal impedance depends on the thermal conduction efficiency of the chip and the environment, and the thermal impedance can be reduced by adding a heat sink or a fan The second is to reduce PD: reduce the total power consumption by optimizing the FPGA design. The following two parts are introduced

A. Power consumption estimation

There are several common schemes for power consumption evaluation of Xilinx FPGA: Xilinx’s own XPE (can be downloaded on the xilinx official website: http://www.xilinx.com/power, it is an excel-based tool), TI’s WEBENCH (It seems that there is only FPGA part, no ARM part), Vivado software, development board actual measurement evaluation, etc. These solutions can be customized according to their own peripherals, which is convenient and flexible.

Before a low-power design, a power evaluation is required. XPE is mainly used for power consumption estimation in the early stage of the project, in the system design, and the RTL code is not perfected. After the design is synthesized and implemented, the power consumption analysis tool that comes with vivado can be used to accurately calculate the power consumption. Open the design after comprehensive implementation, click report power to get the result of power analysis.

B. Power optimization

Regarding FPGA low-power design, we can start from two aspects: one is algorithm optimization; the other is optimization of FPGA resource utilization efficiency.

Algorithm optimization

Algorithm optimization can be divided into two levels: implementation structure and implementation method. First of all, it is necessary to design an optimized algorithm implementation structure, and design an optimized structure to minimize resource occupation, and of course power consumption can be minimized, but it is also necessary to ensure performance, so that FPGA design can be achieved in terms of area and speed. Both can be accommodated. For example, when choosing to use a pipeline structure or a state machine structure, all the states of the pipeline structure are working continuously at the same time, while only one state of the state machine structure is enabled. Obviously, the pipeline structure consumes more power, but its data throughput rate And the system performance is better, so it is necessary to choose one reasonably, so that the system can be balanced between area and speed.

Another level is the specific implementation method. Among all the signals that absorb power in the design, the clock is the culprit. Although a clock may run at 100MHz, signals derived from this clock typically run at a smaller fraction of the master clock frequency (say 12% to 15%). In addition, the fan-out of the clock is generally high. These two factors show that in order to reduce power consumption, the clock should be carefully studied. First, if a portion of the design can be inactive, consider disabling clock tree flips instead of using clock enables. A clock enable will prevent unnecessary flipping of registers, but the clock tree will still flip, consuming power. Second, isolate the clock to use the minimum number of signal regions. Unused clock tree signal regions are not toggled, reducing the load on that clock network.

Resource usage efficiency optimization

Resource utilization efficiency optimization is a method that can optimize power consumption when using some resources inside the FPGA (such as BRAM, DSP slice). FPGA dynamic power consumption is mainly reflected in the power consumption of memory, internal logic, clock, I/O, etc.

Among them, memory is a major power consumer, such as the memory unit Block RAM in xilinx FPGA, so some power consumption optimization methods for BRAM are mainly introduced.

Although only 7% of BRAM is used in the figure below, its power consumption of 0.614W accounts for 42% of the total design, so optimizing the power consumption of BRAM can effectively reduce the dynamic power consumption of FPGA

Here’s how to optimize BRAM power consumption:

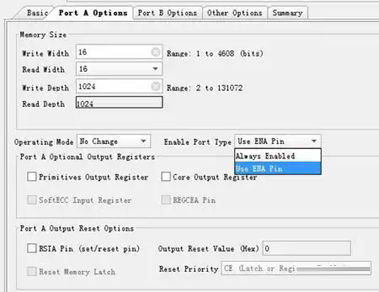

Use “NO CHANGE” mode: when BRAM is configured as True Dual Port, you need to select the port operation mode: “Write First”, “Read First” or “NO CHANGE” to avoid conflict between read and write operations, as shown in Figure 6 As shown; “NO CHANGE” means that BRAM does not add additional logic to prevent read and write conflicts, so it can reduce power consumption, but the designer needs to ensure that no read and write conflicts will occur when the program is running.

After setting to “NO CHANGE”, the power consumption of BRAM is reduced from 0.614W to 0.599W, because only 7% of BRAM is used. If a large amount of BRAM is used in the design, the effect can be more obvious.

Control “EN” signal: There is a clock enable signal in the port of BRAM, which can be enabled in the port setting, and it is connected with the read/write signal when the module is instantiated, so optimization can make the BRAM without read/write Stops work during operation, saving unnecessary power consumption.

The BRAM power consumption is reduced to 0.589W after controlling the “EN” signal optimization.

Depth of spelling: When a large amount of memory is used in the design, it is necessary to splicing multiple blocks of BRAM. For example, the depth of 32K, the width of 32-bit, and the storage capacity of 32K*32Bit are required, but how to configure a single block of BRAM is a problem. 7 series FPGA is 36Kb BRAM, of which 32Kb capacity is generally used, so it can be configured as 32K*1-bit or 1K*32-bit. When multiple BRAMs are spliced, the former is the “split width” in the figure below, and the latter is “Fighting depth”. When the two structures are working, all the BRAMs in the “split width” structure need to be read and written at the same time; while the “split depth” structure only needs one of the BRAMs to read and write, so when low power consumption is required, the “split depth” structure is used. “structure. However, it should be noted that the “split depth” structure requires additional data selection logic, which increases the number of logic layers. In order to reduce power consumption, both area and performance are sacrificed.

Power on and off sequence

1. power-on sequence

FPGAs often require multiple supply voltages and require a certain power-up/power-down sequence. Sequential power-up helps limit inrush current during power-up. Neglecting the device’s power sequencing requirements can result in device damage or latch-up, resulting in FPGA device failure. There are three types of power-up sequences: synchronous tracking, sequential tracking, and ratio tracking.

For each series of FPGA chips, the power-on sequence of each internal functional module is generally independent of each other, and each functional module has internal sequence requirements. For details, please refer to the data sheet of each device, which will have detailed sequence constraints.

2. Ascending monotonicity

During start-up, it is important that the supply voltage maintain a monotonic ramp to ensure successful device turn-on. General FPGAs give strict voltage monotonous rise requirements, that is, the power supply voltage should continuously rise to the set voltage regulation value, and no drop should occur in the middle. If the power supply does not provide enough output power, it will cause a drop

3. Power-on time

Most FPGAs specify minimum and maximum start-up voltage rise rates, and the power supply achieves soft-start by gradually increasing the current limit during start-up. Soft-start slows the rate of rise of the supply voltage and also reduces the peak inrush current injected into the FPGA. A typical power supply can use a soft-start capacitor connected to the pin to set the soft-start time.

4. Power-down sequence

The power-off sequence also needs to be controlled. The standard sequence is to reverse the power-on sequence.

5. Sequence control for special cases

There are often cases where other CPUs such as FPGA and ARM are interconnected. In order not to damage the device, the power-on sequence of FPGA and ARM must meet both their own power-on sequence requirements and the other party’s power-on sequence requirements. The situation can be handled as follows:

When FPGA and ARM each use their own configuration files: since IO is in the input state when ARM is in reset state, and FPGA needs to complete the configuration to determine its IO state, so ARM and FPGA can perform their own power-on sequences. After the power-on sequence of the ARM is completed, it is in the reset state, so that the IO is in the input state. When the FPGA is powered on, the configuration is performed. After the configuration is completed, the ARM is given a configuration completion signal. This signal releases the reset of the ARM and sets the corresponding IO state. There will be no IO conflict, nor will it affect the FPGA startup sequence, nor will it cause the FPGA interface to have a latch-up effect.

When the FPGA uses ARM to provide the configuration file, there will be no IO conflict, because the FPGA releases the reset, and before the configuration, the IO is in a high-impedance state, and the FPGA does not have a configuration file and will not set the IO state.

Power scheme

At present, the common power supply solutions for FPGA include the use of single-channel LDO, single-channel DC/DC, single Power Module, PMIC, etc.

1. LDO

LDOs should be used if board space is available, low output noise is important, or if the system requires fast response to inputs and transients. The LDO provides low to medium output current. The input capacitor typically cuts off the impedance and noise input to the LDO. LDOs also require a capacitor at the output to handle system transient response and provide stability.

2. SMPS

Switching power supplies have advantages when design efficiency is critical and the system requires large output currents. Switching power supplies offer higher efficiency than LDOs, but their switching characteristics make them more sensitive to noise. Unlike LDOs, switching power supplies require the use of inductors and may require a transformer for DC-DC conversion, which requires more space on the PCB.

3. Power Module

Power Module can save yourself from building peripheral circuits, and the modules designed by manufacturers generally have better performance (higher efficiency and lower ripple) than those designed by themselves, but power modules are generally selected when the current demand is relatively large.

4. PMIC

Due to the wide application of FPGA, there are more and more dedicated PMICs for FPGA, which can well meet the needs of specific FPGA chips in terms of output voltage, number of channels, and output current. It has advantages in other respects.

The above is the power supply introduction for Xilinx FPGA, mainly including the type of power supply, voltage requirements, power consumption analysis, power-on and power-on sequence, power supply implementation, etc.

Haoxinshengic is a pprofessional FPGA and IC chip supplier in China. We have more than 15 years in this field。 If you need chips or other electronic components and other products, please contact us in time. We have an ultra-high cost performance spot chip supply and look forward to cooperating with you.

If you want to know more about FPGA or want to purchase related chip products, please contact our senior technical experts, we will answer relevant questions for you as soon as possible

Our Products