What are the advantages of ARM+FPGA architecture?

In recent years, with the continuous development of the world and the advancement of science and technology, it has become increasingly difficult for a single ARM processor to meet the functional requirements of industrial sites. In particular, industries such as energy and power, industrial control, and smart medical care usually require a processor platform with an ARM+FPGA architecture to achieve specific functions. For example, multi-channel/high-speed AD acquisition, multi-channel network port, multi-channel serial port, multi-channel/high-speed parallel DI/DO, high-speed data parallel processing, etc. What are the advantages of the ARM+FPGA architecture?

ARM: Rich interface resources, low power consumption, good at multimedia display, logic control, etc.

FPGA: Good at multi-channel or high-speed AD acquisition, interface expansion, high-speed signal transmission, high-speed data parallel processing, etc.

Therefore, the ARM+FPGA architecture can bring comprehensive comparative advantages in terms of performance, cost, and power consumption. ARM and FPGA can perform their own duties and give full play to the unique advantages of the original architecture, and they can also cooperate with each other to solve more complex problems. For higher discrete ARM+FPGA occasions that are not sensitive to cost and require communication speed, the PCIe communication interface is generally used. However, for cost-sensitive discrete ARM+FPGA applications, the PCIe communication interface keeps the cost of the FPGA chip high.

For many industrial fields such as energy and power, industrial control, etc., what is really needed is a solution with competitive performance and cost. It is required to achieve high-speed communication between ARM and FPGA, and to achieve optimal cost, and it is best to be based on Domestic program. In the context of this demand, HAOXINSHENG Technology provides three solutions based on domestic ARM and low-cost FPGA high-speed communication.

Hardware Platform Introduction

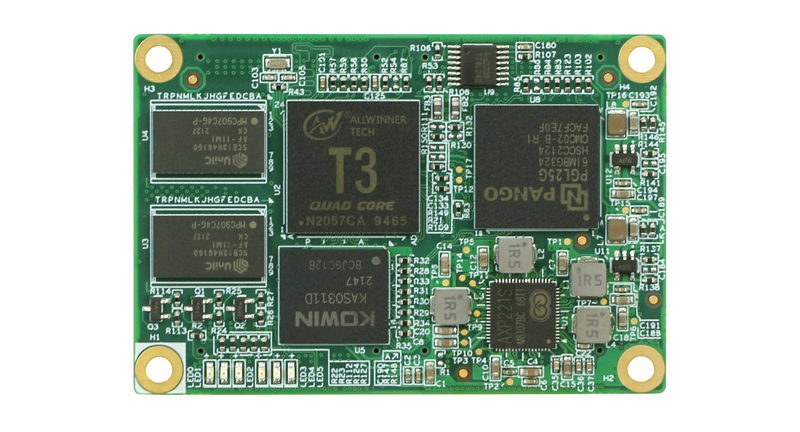

HAOXINSHENG Technology TLT3-EVM/TLA40i-EVM is a 4-core ARM Cortex-A7 industrial evaluation board designed based on T3/A40i processor. Both T3 and A40i are pin to pin compatible. The evaluation board is rich in interface resources, leading out dual network ports, dual CAN, dual USB, dual RS485 and other communication interfaces, onboard Bluetooth, WIFI, 4G (optional) modules, and also leads out MIPI LCD, LVDS LCD, TFT LCD , HDMI OUT, CVBS OUT, CAMERA, LINE IN, H/P OUT and other audio and video multimedia interfaces, support dual-screen different display, Mali400 MP2 GPU, 1080P@45fps H.264 video hardware encoding, 1080P@60fps H.264 video hardware decoding, and supports SATA mass storage interface.

The core board has been verified by professional PCB Layout and high and low temperature testing, which is stable and reliable, and can meet various industrial application environments. Most of the components on the evaluation board adopt current mature solutions, which is convenient for users to quickly conduct product solution evaluation and technology pre-research.

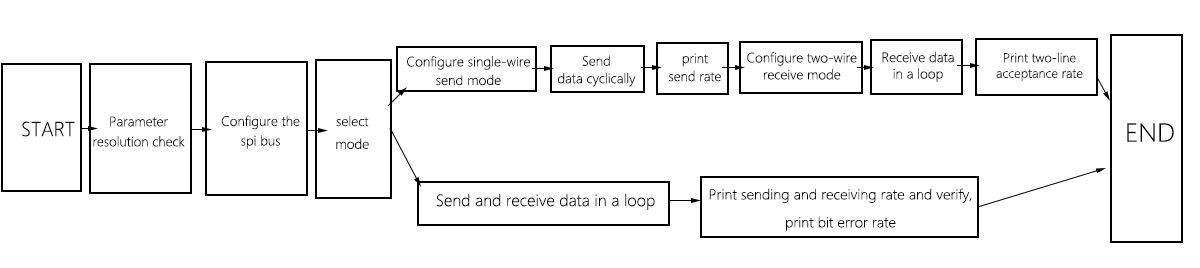

1. spi_rw case

Case Description

Case function: It mainly demonstrates the SPI communication between T3/A40i (ARM Cortex-A7) and PGL25G/Spartan-6 (FPGA) processor.

The ARM side realizes the SPI Master function a. Open the SPI device node, such as: /dev/spidev0.0. b. Use ioctl to configure the SPI bus, such as SPI bus polarity and phase, communication rate, data word length, etc. c. Select the mode as single-line mode or dual-line mode. When the SPI bus is in two-wire mode, sending data is single-wire mode, and receiving data is two-wire mode. d. Send data to the SPI bus, and read data from the SPI bus. (Note: If the single transfer data is larger than 64Byte, the driver will automatically enable the DMA transfer function.) e. Print the sending and receiving rates. f. Verify the read and write data, and then print the bit error rate. The FPGA side realizes the SPI Slave function a. The FPGA saves the 2KByte data sent by the SPI Master to the BRAM. b. When the SPI Master initiates read data, the FPGA reads 2KByte from the BRAM and transmits it to the SPI Master through the SPI bus. c. When the SPI bus is in two-wire mode, receiving data supports two-wire mode, but sending data does not support two-wire mode

Test Results

(1) SPI single-wire mode According to the official data sheet, the theoretical value of the SPI bus communication clock frequency is up to 100MHz. This test specifies that the SPI bus communication clock frequency is the maximum value of 100MHz, then the theoretical rate of the SPI single-wire mode is: (100000000/1024/1024/8)MB/s ≈ 11.92MB/s. The measured SPI single-wire mode write rate is: 10.924MB/s, and the SPI single-wire mode read rate is: 10.924MB/s.

(2) SPI dual-wire mode According to the official data sheet, the theoretical value of the SPI bus communication clock frequency is up to 100MHz. This test specifies that the SPI bus communication clock frequency is the maximum value of 100MHz, then the theoretical rate of SPI single-wire mode is: (100000000/1024/1024/8)MB/s ≈ 11.92MB/s; then the theoretical rate of SPI dual-wire mode is: ( 100000000/1024/1024/4)MB/s ≈ 23.84MB/s. The measured SPI single-wire mode write rate is 11.631MB/s, and the SPI dual-wire mode read rate is 17.807MB/s.

2. rt_spi_rw case

Case Description

Case function:

Based on Linux-RT system, demonstrate the SPI communication (single-wire mode) between T3/A40i (ARM Cortex-A7) and PGL25G/Spartan-6 (FPGA) processor.

The ARM side implements the SPI Master function

- Open the SPI device node. Such as: /dev/spidev0.0.

- Use ioctl to configure the SPI bus. Such as SPI bus polarity and phase, communication rate, data word length, etc.

- Create a real-time thread.

- Send data to the SPI bus, and read data from the SPI bus.

- Print sending and receiving rates and transmission time.

- Verify the read and write data, and then print the bit error rate.

FPGA side realizes SPI Slave function

- FPGA saves 2KByte data sent by SPI Master to BRAM.

- When the SPI Master initiates read data, the FPGA reads 2KByte from the BRAM and transmits it to the SPI Master through the SPI bus.

Test Results

(1) Non-polling mode According to the official data sheet, the theoretical value of the SPI bus communication clock frequency is up to 100MHz. This test specifies that the SPI bus communication clock frequency is a maximum of 100MHz, and the theoretical rate is: (100000000/1024/1024/8)MB/s ≈ 11.92MB/s. The measured minimum time consumption for transmitting 4Byte data is 49us, the maximum time consumption is 662us, and the average time consumption is 227us; the write rate is 0.017MB/s, and the read rate is 0.017MB/s.

(2) Polling method According to the official data sheet, the theoretical value of the SPI bus communication clock frequency is up to 100MHz. This test specifies that the SPI bus communication clock frequency is a maximum of 100MHz, and the theoretical rate is: (100000000/1024/1024/8)MB/s ≈ 11.92MB/s. The measured minimum time consumption for transmitting 4Byte data is 14us, the maximum time consumption is 59us, and the average time consumption is 14us; the write rate is 0.239MB/s, and the read rate is 0.239MB/s.

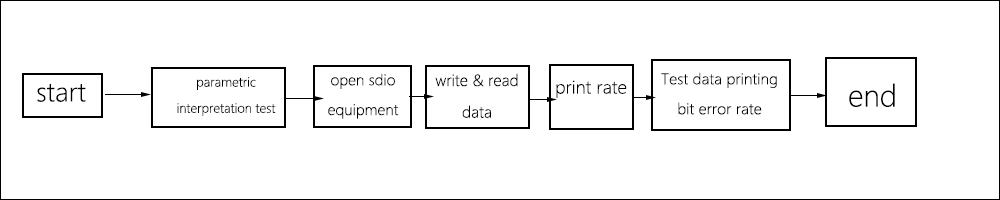

3. sdio_test case

Case Description

Case function:

Demonstrate SDIO communication between T3/A40i (ARM Cortex-A7) and PGL25G/Spartan-6 (FPGA) processor. ARM side realizes the SDIO Master function a. Open the SDIO device node, such as: /dev/generic_sdio0. b. Send data to SDIO bus, and read data from SDIO bus. c. Print the send and receive rates. d. Verify the read and write data, and then print the bit error rate.

FPGA side realizes SDIO Slave function

- FPGA saves the 2KByte data sent by SDIO Master to BRAM.

- When SDIO Master initiates read data, FPGA reads 2KByte from BRAM and transmits it to SDIO Master through SDIO bus.

Test Results

This test specifies that the SDIO bus communication clock frequency is 25MHz (up to 50MHz), then the theoretical communication rate is: (25 x 4 / 8)MB/s = 12.5MB/s. The measured write rate is 5.113MB/s, the read rate is 5.440MB/s, and the bit error rate is 0.0%.

4. csi_test case

Case Description

Case function:

Demonstrate the CSI communication case between T3/A40i (ARM Cortex-A7) and PGL25G/Spartan-6 (FPGA) processor.

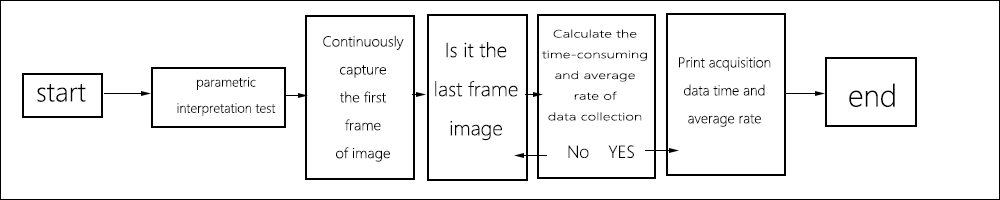

ARM-side functions a) Based on the Linux subsystem V4L2. b) Through the CSI bus, collect the specified frame number data. c) Calculate the total time-consuming. d) Print the average acquisition rate and verify the data of the last frame of image.

FPGA side function a) Write test data (0x00 ~ 0xFF) into FIFO. b) Read the data from the FIFO, and send it to the ARM side through the CSI bus in the form of lines and frames with a resolution of 1024 x 512. The CSI bus used is CSI0, the highest supported resolution is 1080P30, and the data bit width is 8bit. The functional block diagram and program flow chart are shown in the figure below.

Test Results

The FPGA side sets the CSI_PCLK to 65MHz, and the clock FIFO_WR_CLK for writing the test data into the FIFO is set to 59MHz. Since the FPGA side needs to write the data into the FIFO and then read it from the FIFO and send it, the interval between each line and each frame will be affected by the rate of FIFO writing, so the actual theoretical transmission bandwidth of CSI communication should be: (59MHz x 8bit / 8)MB/s = 59MB/s. The measured transmission rate is 55.1MB/s, and the bit error rate is 0.0%

Haoxinshengic is a pprofessional FPGA and IC chip supplier in China. We have more than 15 years in this field。 If you need chips or other electronic components and other products, please contact us in time. We have an ultra-high cost performance spot chip supply and look forward to cooperating with you.

If you want to know more about FPGA or want to purchase related chip products, please contact our senior technical experts, we will answer relevant questions for you as soon as possible

Our Products